Apple liberó parte del código de LLVM y esto permitió conocer en detalle varias características del procesador A7 de 64 bits que actualmente potencia al iPhone 5S.

Lo interesante es comparar con la tecnología utilizada en el A6, una de las críticas hacia el A7 el día de su lanzamiento fue que no aumentaba la cantidad de núcleos y sólo ofrecía 64 bits como diferencial, pero por dentrgo los cambios eran más notables y si bien en performance no es muy grande la diferencia, sí lo es en arquitectura.

El A7 con los núcleos Cyclone es más parecido a un Haswell de Intel que a un Krait de Qualcomm y eso es más que relevante. El tema de los 64 bits es anecdótico y con utilidad a futuro, estos cambios también pero se notará su diferencia en las generaciones inmediatamente posteriores. La razón es que un núcleo más complejo no puede utilizar un clock tan acelerado… hasta que se cambia el proceso de fabricación. Y eso es lo que se le viene a Apple para su siguiente generación al pasar al proceso de 20nm de TSMC.

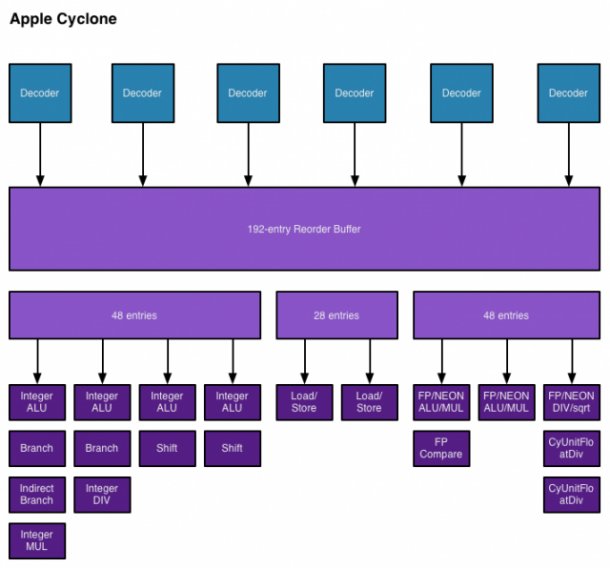

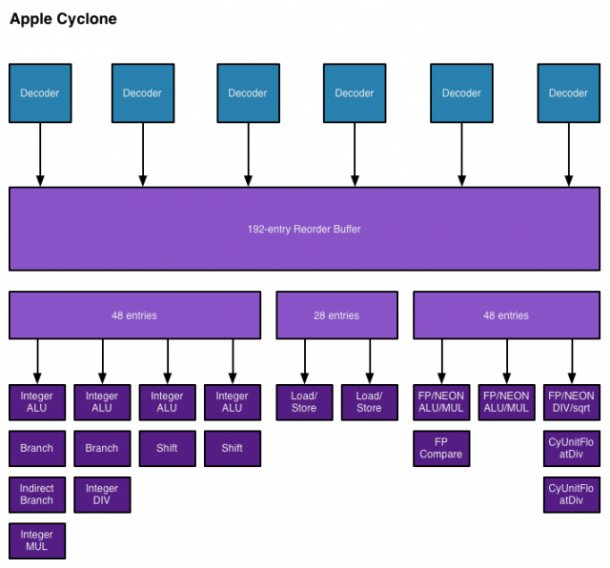

En detalle un Cyclone puede procesar hasta seis hilos simultáneamente en un diseño out-of-order, el doble que los otros diseños, el buffer de reorden pasó de 45 micro-ops a 192 micro-ops necesario para poder manejarlo así, esto agrega dos ciclos más, 16 en vez de 14, pero duplicaron las unidades ALU de enteros, además de extender hasta una tercer caché con la L3.

La diferencia no se nota en los clocks actuales pero la realidad es que fácilmente un A7 con un clock más fuerte podría desplazar sin problemas a un Octa Core aun con menos núcleos, el tema es que en el proceso actual no se puede sin quemara la batería. Lo ideal será en el ciclo A8-A9 al pasar a los ya mencionados 20nm.

| Apple Custom CPU Core Comparison | ||||||

| Apple A6 | Apple A7 | |||||

| CPU Codename | Swift | Cyclone | ||||

| ARM ISA | ARMv7-A (32-bit) | ARMv8-A (32/64-bit) | ||||

| Issue Width | 3 micro-ops | 6 micro-ops | ||||

| Reorder Buffer Size | 45 micro-ops | 192 micro-ops | ||||

| Branch Mispredict Penalty | 14 cycles | 16 cycles (14 – 19) | ||||

| Integer ALUs | 2 | 4 | ||||

| Load/Store Units | 1 | 2 | ||||

| Load Latency | 3 cycles | 4 cycles | ||||

| Branch Units | 1 | 2 | ||||

| Indirect Branch Units | 0 | 1 | ||||

| FP/NEON ALUs | ? | 3 | ||||

| L1 Cache | 32KB I$ + 32KB D$ | 64KB I$ + 64KB D$ | ||||

| L2 Cache | 1MB | 1MB | ||||

| L3 Cache | – | 4MB | ||||

Por ejemplo otra limitación era lanzarlo con memorias RAM de apenas 1GB, es un procesador que podría manejar tranquilamente 16GB si quieren, pero Apple fue extremadamente conservadora en su primer versión. Si proyectamos este diseño a futuro es plausible la idea de una total independencia de la empresa de los proveedores de microprocesadores para la mayoría de sus líneas.

Es decir, no sería de extrañar ver una Apple con procesador propio y no me refiero ni a los iPhone ni iPads sino las Macbook, algo que se ve a lo lejos pero que necesita sí o sí de una performance similar a la de un Haswell para tener sentido. Al menos en la arquitectura general se parecen.

Intel, el principal “complicado” ante estas maniobras de Apple ya ha hecho algo parecido, pasar en un sólo ciclo a tres versiones con los Saltwell/Silvermont/Airmont en el rango de apenas dos años y sigue sin poder proveer a sus clientes móviles en la cantidad que lo hace Qualcomm. Apple optó por sus propios diseños, una medida nada extraña para alguien con semejante billetera, pero ¿Podrá Intel convencerla de volver? muy difícil, ahora Apple tiene el control real.

Por otra parte el cambio de proceso a 20nm cambiará notablemente las velocidades conservadoras del A7 (entre 1.3 y 1.5GHz) y lo hará más competitivo con los Exynos y Tegras, pero con estas modificaciones de arquitectura probablemente no necesite superar los 2GHz para lograr una mayor eficiencia por ciclo, y esa será una de las mayores ventajas en el largo plazo.

Via Extremetech