Es difícil explicar el IBM Telum en un título más aun en un artículo entero porque para muchos los mainframes no existen hace tiempo pero no están más que equivocados: existen y siguen siendo muy usados.

El concepto del mainframe nunca desapareció y prácticamente toda la infraestructura de la nube funciona como un gran mainframe, el procesamiento sucede en el servidor, no en nuestro equipo local. Acostúmbrense, lo llamamos nube pero muchas veces opera exactamente como un mainframe 😀

Volviendo a este nuevo procesador de IBM encontramos algunas cosas muy locas e interesantes en su diseño. Tengan en cuenta que son equipos pensados para tener un servicio casi perfecto, estos mainframes tienen un uptime donde la “baja” se mide en microsegundos, no una hora o dos, aquí nada debe caerse jamás.

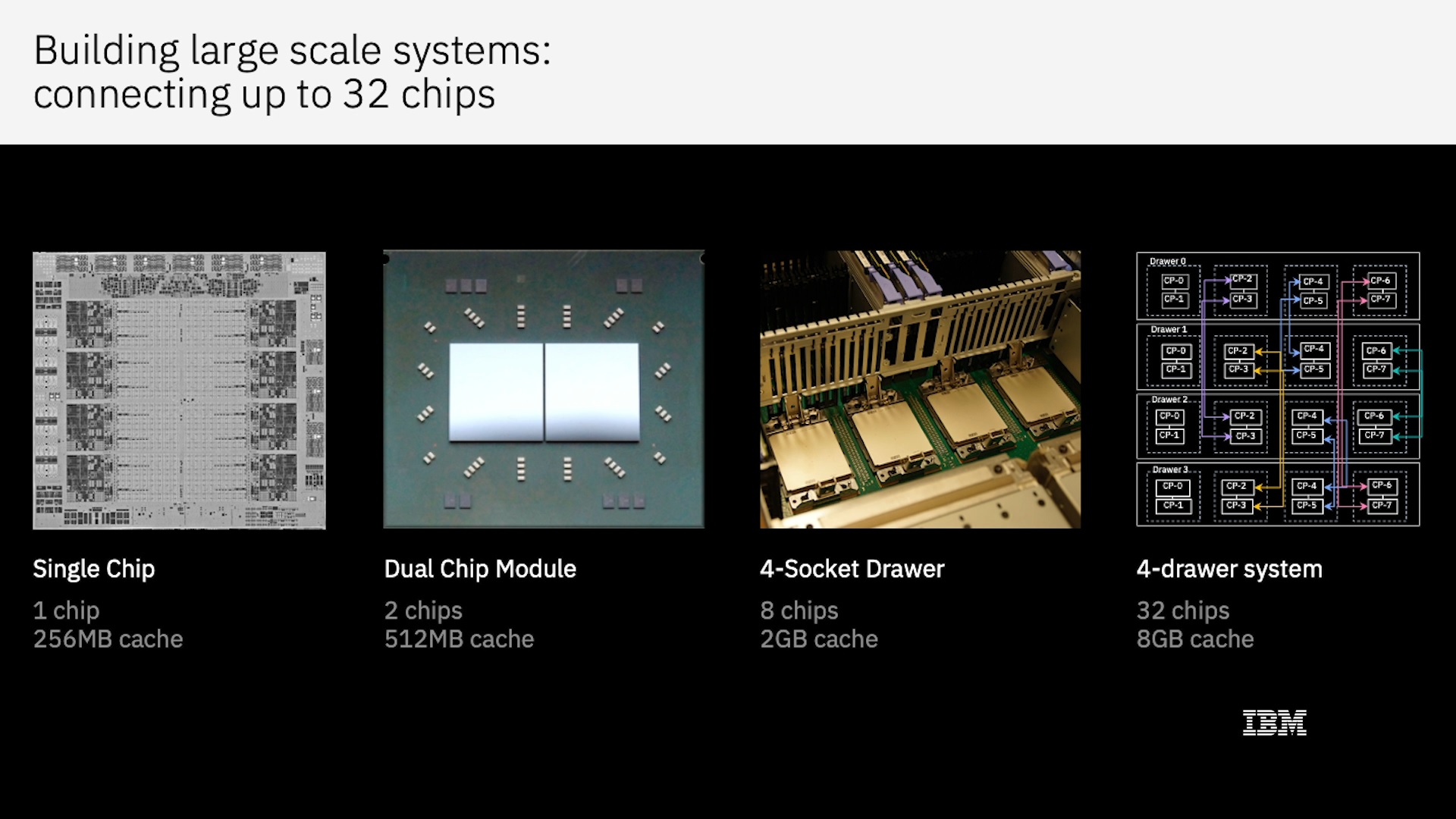

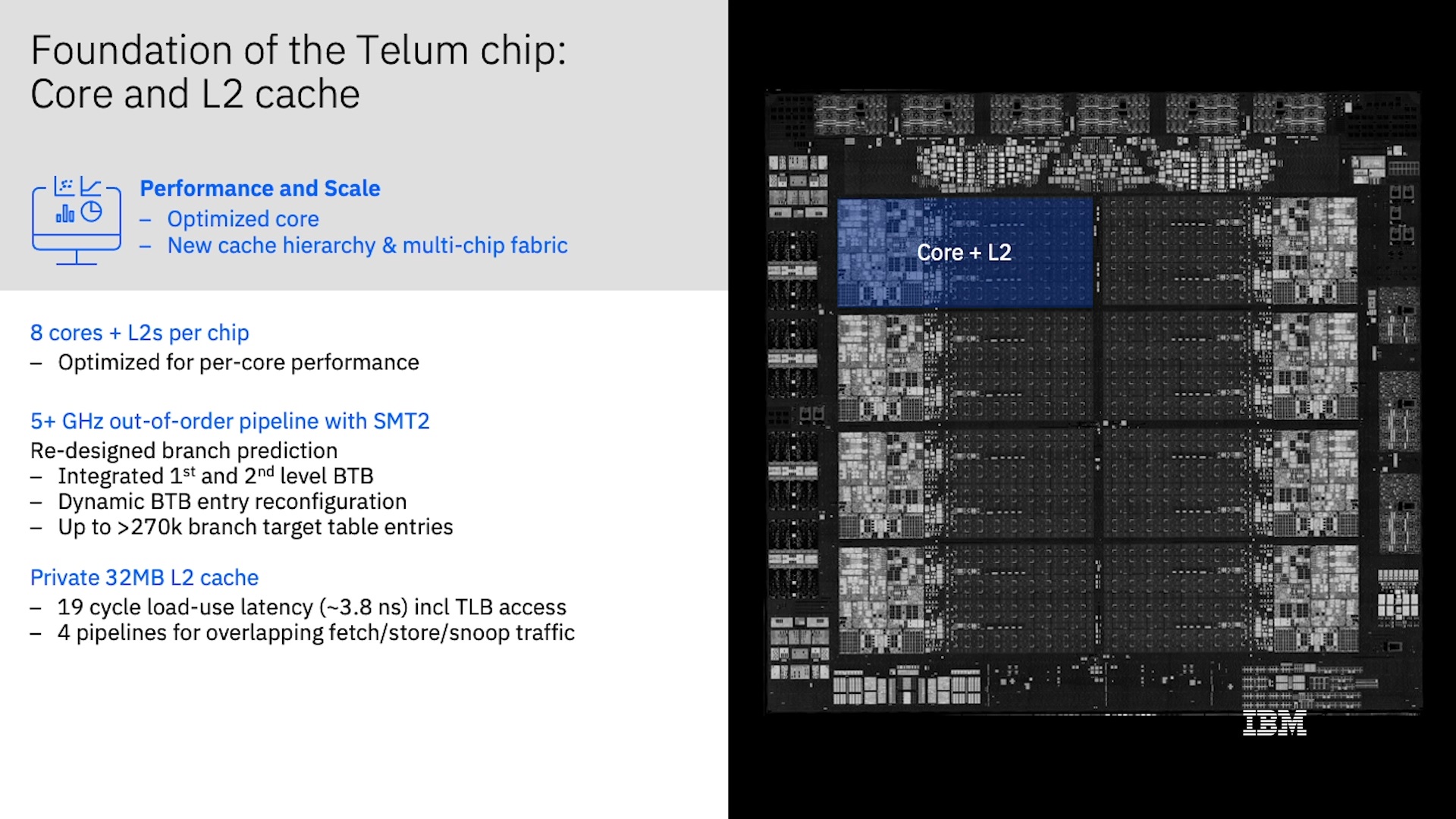

La arquitectura IBM Z lleva años existiendo, el último era el Z15 fabricado a 14nm, este nuevo Telum está fabricado en el proceso de 7nm de Samsung pero tomando la idea de chiplets de AMD, así que ocho núcleos entran en un procesador y dos procesadores se combinan en un paquete. Todos los procesadores son idénticos, no hay un system controller, estos paquetes Telum se agrupan de a cuatro en un “drawer” y cuatro de estos “drawers” conforman un sistema.

Si hicieron las cuentas esto provee 256 núcleos en 32 CPUs, y a todo esto el clock base está en 5GHz, una barbaridad. Ese es el clock base y por ende logra consistencia en las latencias siendo predecible. Algo imprescindible en este escenario.

Si hicieron las cuentas esto provee 256 núcleos en 32 CPUs, y a todo esto el clock base está en 5GHz, una barbaridad. Ese es el clock base y por ende logra consistencia en las latencias siendo predecible. Algo imprescindible en este escenario.

https://www.youtube.com/watch?v=TRBgBbvYiQw

Cuestión de Caché

Ahora bien, hasta aquí suena igual a muchas cosas que hemos visto pero IBM sumó una serie de memorias caché que hay que explicar por separado.

La idea fue remover completamente la L4 (eran 960MiB) y también la L3 ¿Cómo? Pues bien, el diseño cambia radicalmente aquí y cada núcleo tiene una L2 privada de 32MiB y listo, nada más. Ahora bien ¿Privada? No tanto, porque esa L2 puede ser virtual y aquí se complica la cuestión.

No todos los núcleos necesitan usar la L2 completamente y otro a su lado puede tomar prestada alguna línea de memoria y usarla como una L3 virtual. Si hay lugar libre se va usando la L2 de otro núcleo como L3 propia y esto lleva la cuenta hasta 256MiB por cada procesador Telum.

Ahora bien, esto suena genial pero no se quedaron en la L3: si se necesita liberar esa L3 prestada se puede usar la L2 de otro procesador a un lado, esta se virtualiza como L4, sube la latencia, claro, pero ahora se dispone de 8GB entre todos los paquetes de procesadores!

Ahora bien, esto suena genial pero no se quedaron en la L3: si se necesita liberar esa L3 prestada se puede usar la L2 de otro procesador a un lado, esta se virtualiza como L4, sube la latencia, claro, pero ahora se dispone de 8GB entre todos los paquetes de procesadores!

Esto funcionará? Por el momento no tengo la más mínima idea, suena demasiado complejo como para que funcione pero ¿Y si lo logran? Ah, maravilla porque abre una caja de pandora para el diseño de todos los procesadores de todas las marcas.

Como dicen en Anandtech: Magia. Este es el futuro de las cachés.