A principios de este año, SK hynix y TSMC decidieron unir fuerzas para desarrollar y fabricar matrices base para la memoria HBM4.

Aunque en su momento no dieron muchos detalles, esta semana en el Simposio de Tecnología Europea 2024, TSMC reveló que utilizarán sus avanzadas tecnologías de proceso 12FFC+ (clase de 12nm) y N5 (clase de 5nm) para crear estas matrices base.

“Estamos colaborando con socios clave en memoria HBM, como Micron, Samsung y SK hynix, para integrar HBM4 con nodos avanzados”, explicó el Director Senior de Diseño y Plataforma Tecnológica de TSMC. “El die base 12FFC+ es rentable y puede alcanzar el rendimiento de HBM, mientras que el die base N5 ofrece aún más lógica con un consumo de energía significativamente menor a velocidades HBM4”.

La tecnología N5 de TSMC es una de las más avanzadas del mercado y se utiliza en la fabricación de los mejores CPUs y GPUs, por lo que emplearla en memoria es un gran avance.

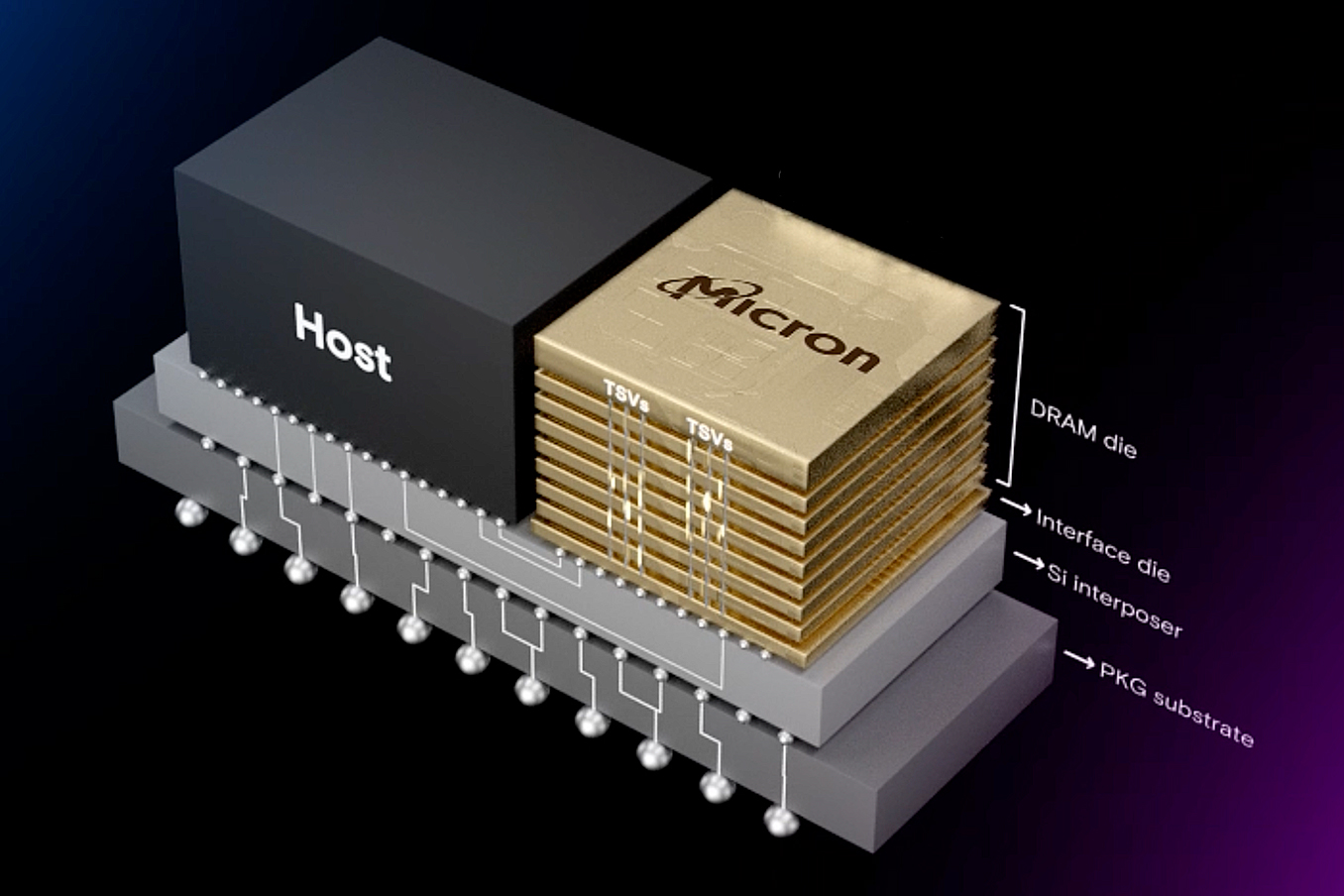

Este nodo avanzado permite empaquetar más lógica y características en el die base HBM4 y habilita pitches de interconexión extremadamente finos (de 9 a 6 micrones), cruciales para la unión directa en chips lógicos, mejorando así el rendimiento de la memoria para procesadores de IA y HPC.

Los matrices base fabricados con el proceso 12FFC+ de TSMC (derivado de la ya consolidada tecnología FinFET de 16nm) permitirán construir pilas de memoria HBM4 de 12 y 16 capas, con capacidades de 48 GB y 64 GB, respectivamente.

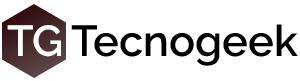

El 12FFC+ posibilitará la creación de matrices base rentables que utilizarán intercaladores de silicio para conectar la memoria a los procesadores anfitriones.

TSMC también está mejorando sus tecnologías de empaquetado, específicamente CoWoS-L y CoWoS-R, para soportar la integración de HBM4. Estos métodos avanzados permiten construir intercaladores de hasta ocho tamaños de retícula y facilitan el ensamblaje de hasta 12 pilas de memoria HBM4.

TSMC también está mejorando sus tecnologías de empaquetado, específicamente CoWoS-L y CoWoS-R, para soportar la integración de HBM4. Estos métodos avanzados permiten construir intercaladores de hasta ocho tamaños de retícula y facilitan el ensamblaje de hasta 12 pilas de memoria HBM4.

Los nuevos intercaladores tendrán hasta ocho capas para asegurar un enrutamiento eficiente de más de 2,000 interconexiones, manteniendo la integridad de la señal. Hasta ahora, las pilas experimentales de memoria HBM4 han alcanzado tasas de transferencia de datos de 6 GT/s a 14mA, según una diapositiva de TSMC.

“También estamos optimizando CoWoS-L y CoWoS-R para HBM4”, mencionó el representante de TSMC. “Ambos métodos utilizan más de ocho capas para permitir el enrutamiento de más de 2,000 interconexiones con adecuada integridad de señal. Colaboramos con socios de EDA como Cadence, Synopsys y Ansys para certificar la integridad de la señal del canal HBM4, así como la precisión térmica y electromagnética”.

La colaboración de TSMC con líderes en la producción de memoria como Micron, Samsung y SK hynix, junto con socios de EDA como Cadence, Synopsys y Ansys, es esencial para que los subsistemas de memoria HBM4 se hagan realidad en unos pocos años.

Via Anandtech